FFT FPGA

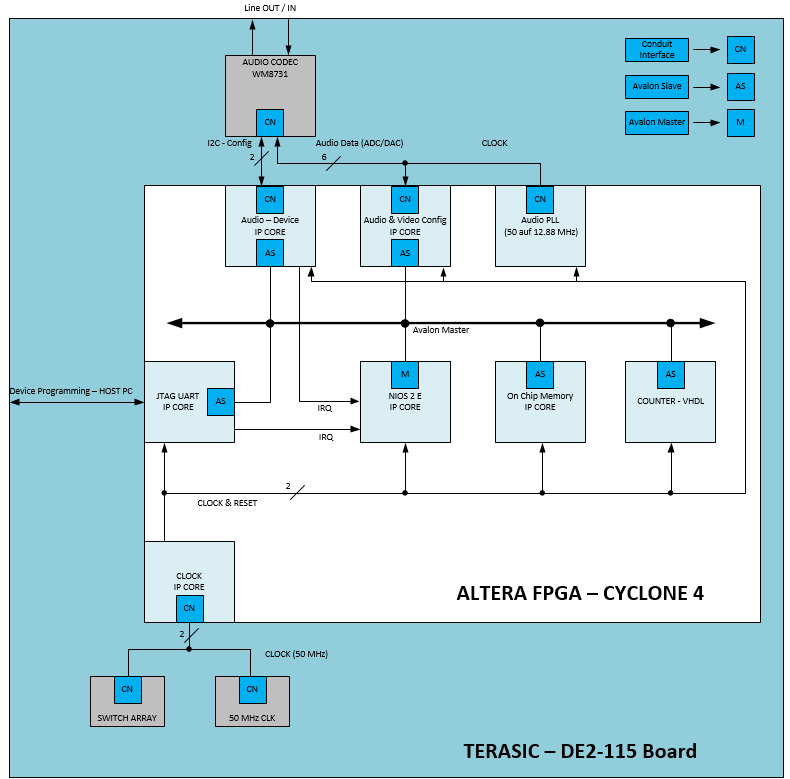

Innerhalb dieses Projektes ist im Rahmen des Wahlmoduls EDS (Entwicklung digitaler Systeme) eine Softcore CPU mittels VHDL auf einem FPGA-Board (DE2-115) implementiert worden, um über diese eine Onlinefrequenzanalyse mittels FFT (Fast Fourier Transformation) eines Audiosignals zu ermöglichen.

Für dieses Vorhaben bietet sich die Softcore-Lösung an, da diese variabel dimensioniert werden kann, vor allem bezüglich des nutzbaren Speichers. Der ASIC Hersteller Altera bietet zu diesem Zwecke eine Softcore CPU (NIOS II) an. Diese wird innerhalb eines Systemdesign-Tools (QSYS) konfiguriert und kann um eigene VHDL Komponenten erweitert werden. Die Programmierung des Prozessors und der FFT erfolgen in C-Code. Auf diese Weise kann ein beliebig komplexes System erschaffen werden, welches die Stärken der Entwicklung von digitalen Schaltungen mittels VHDL und die der klassischen Softwareentwicklung in C-Code verbindet. Das gesamte Projekt, die Dokumentation, die Software (C-Files) und die Quartus Projektdateien sind nachfolgend als Download bereitgestellt.

| Projektdokumentation | download |

| Software (C-Files) | download |

| Quartus Projektdateien | download |

Lukas Wöhle