Verarbeitung des Empfangssignals über einen Komparator

Zur Auswahl stand die Auswertung des Signals über den Audio-Codec des DE2 Boards als auch die Auswertung als rein periodisches Signal mit TTL Pegel über einen der digitalen Eingänge. Da die Charakteristik des Signals bekannt ist und dessen Abweichungen sich in nur einem kleinen Bereich bewegen, wurde beschlossen, das Signal durch eine geeignete Komparatorschaltung weiter zu verarbeiten und dessen Ausgangssignal nach Abgriff über einen digitalen Eingang des DE2 Boards weiter per Software in VHDL auszuwerten.

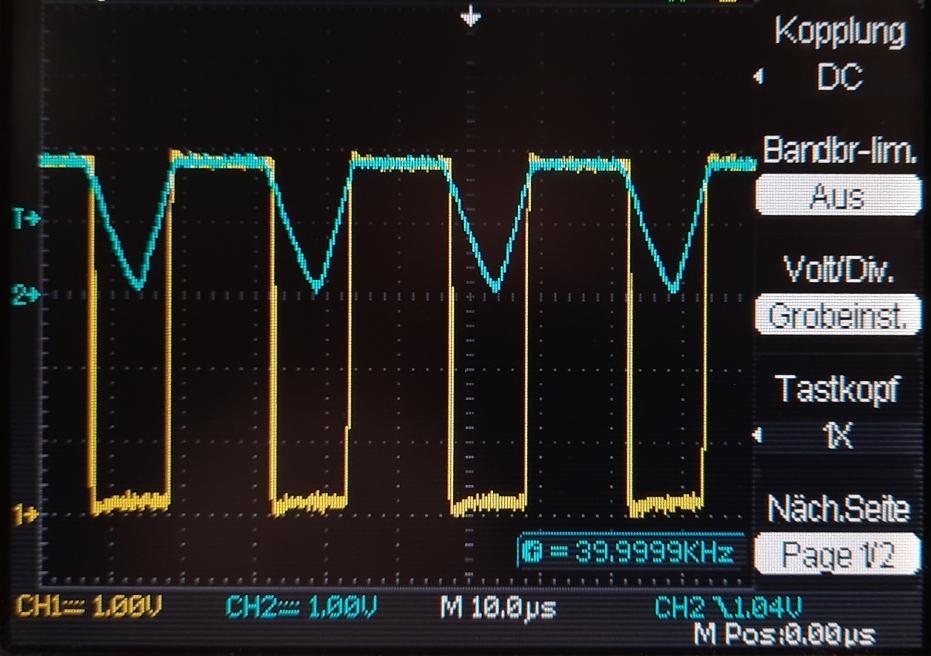

Für die Verarbeitung des Empfangssignals aus dem Abgriff des OP2 Ausgangs wurde ein LM311(D) von STMicroelectronics eingesetzt (LM211.pdf, STMicroelectronics IC Familie LM111/LM211/LM311). Hierbei handelt es sich um einen IC, welcher einen OP mit integrierter Komparatorschaltung darstellt. Im Gegensatz zu der Mehrzahl an OP benötigt der LM311 nicht zwingend eine symmetrische Betriebsspannung sondern kann auch mit 0-5 V betrieben werden. In diesem Modus kann der Komparator zur Erzeugung einer TTL kompatiblen Ausgangsspannung mit einem HIGH-Pegel geringfügig unterhalb der Betriebsspannung von 5 V genutzt werden. Zusätzlich ist der LM311 spezifiziert für Eingangssignale mit Frequenzen von bis zu 1MHz, da er geringe Sättigungskapazitäten besitzt. Daher eignet er sich gut für die Verarbeitung des dargestellten Empfangssignals.

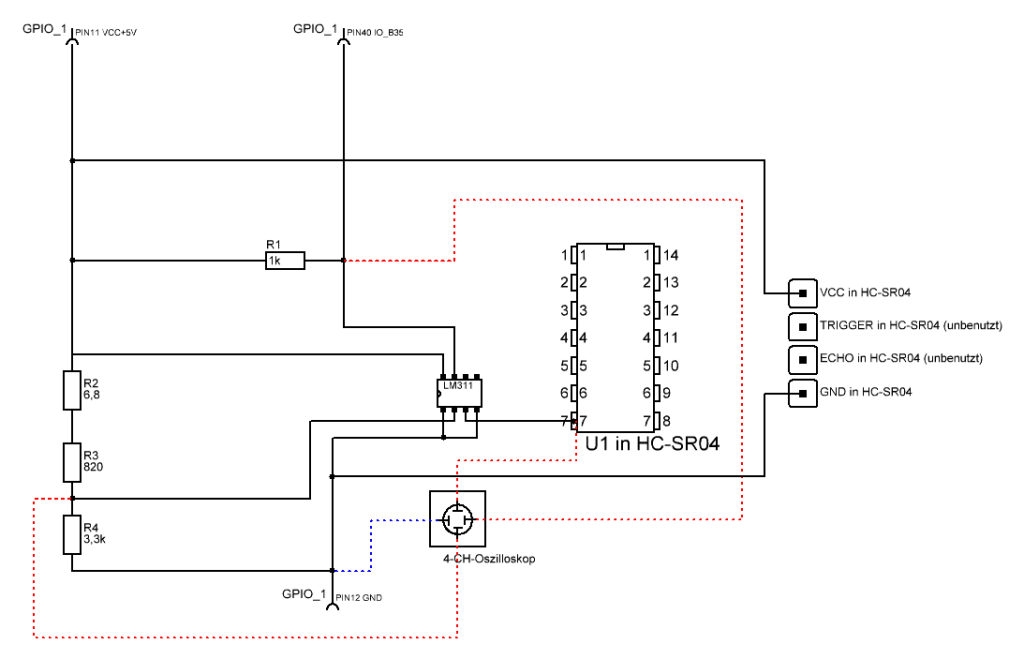

Der LM311 ist als Open Collector ausgeführt und schaltet daher nicht zwischen Versorgungsspannung und GND sondern zwischen Offen und GND, wobei ein geringfügiger Spannungsabfall nach GND erzeugt wird. Für die Nutzung zur Erzeugung eines TTL-Signals muss daher ein Pull-Up Widerstand nach Vcc eingesetzt werden, der von uns als 1 kOhm Widerstand ausgelegt wurde, wodurch der Stromfluss mit 5mA nur 10% des spezifizierten Maximalstroms beträgt.

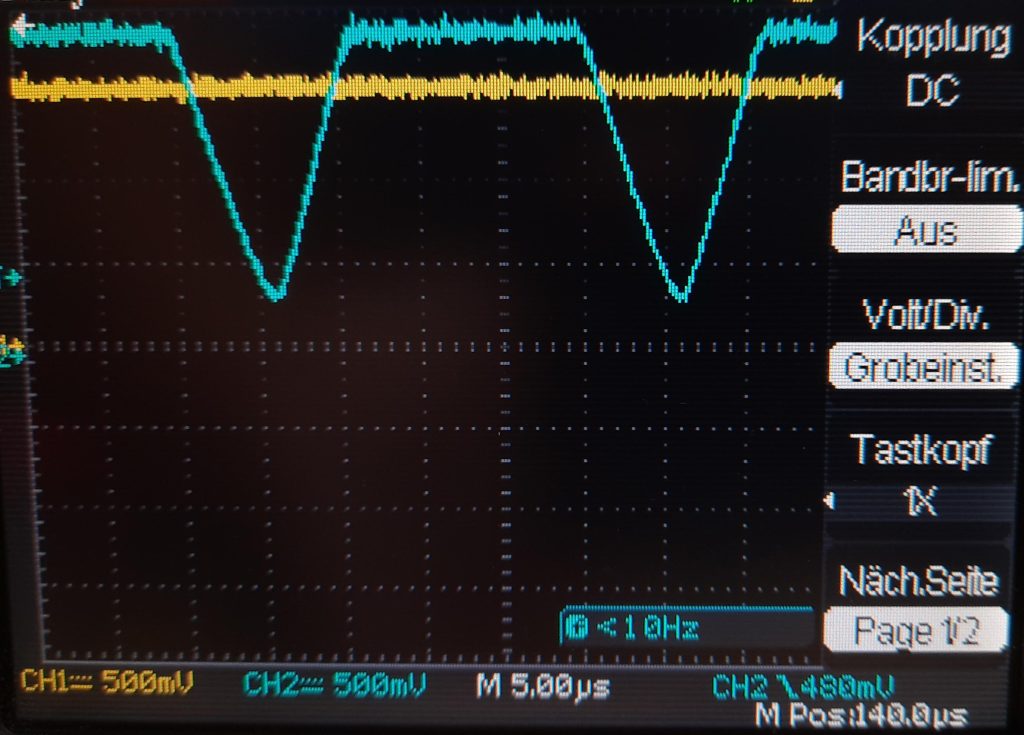

Die Vergleichsspannung wird durch einen Spannungsteiler mit zwei Widerständen erzeugt. Die Spannungskennlinie des LM311 besitzt eine anfängliche Nichtlinearität zwischen 0 und 0,1 V , weshalb die Vergleichsspannung mindestens um diesen Betrag von der Basisspannung des Eingangssignals (hier: ca. 1,9 V) entfernt liegen sollte. Ein unnötig großer Abstand von der Basisspannung ist ebenfalls zu vermeiden, da hierdurch die High-Flanke kurz ausfallen würde, insbesondere bei geringer Empfangsstärke.

Nach Simulation verschiedener Spannungen über ein Labornetzteil wurde die Vergleichsspannung unter Berücksichtigung der genannten Anforderungen auf 1,51 V festgelegt, welche durch einen Spannungsteiler von 3,3 kOhm und 7,62 kOhm (6,8 kOhm+0,82 kOhm) an Vcc 5 V realisiert wurde.

Gegenüber Abbildung „Schwaches Empfangssignal auf CH1“ wurde im finalen Design die Einspeisung von Invertiertem und Nicht-Invertiertem Eingangssignal in den Komparator getauscht, so dass dessen Ausgangssignal invertiert zu dem dort abgebildeten ist und dessen Pegel auf HIGH liegt, wenn sich die Spannung des Empfangssignals unterhalb der Vergleichsspannung befindet. Der sich so ergebende Tastgrad beträgt ca. 40% bei maximalem Empfangssignalpegel und fällt auf 0 bei Unterschreiten der Vergleichsspannung von 1,51 V, in dessen Fall das Signal keine ausreichend stark ausgebildete Amplitude mehr besitzt. Das so gebildete Signal wird über den von uns gewählten GPIO1_35 Pin des JP2 Ports in das Entwicklungsboard eingespeist. Die Spannungsversorgung der HC-SR05 Empfangsplatine und des Komparators geschieht über die +5 V und GND Pins des JP2 Ports.